이재용기사 모아보기 삼성전자 부회장이 온양사업장을 방문해 패키지 기술을 점검한 지 2주만이다.

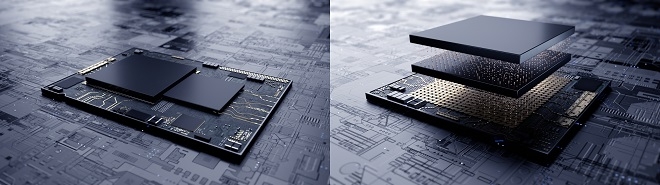

이재용기사 모아보기 삼성전자 부회장이 온양사업장을 방문해 패키지 기술을 점검한 지 2주만이다. 삼성전자는 7나노 EUV 시스템반도체에 3D 적층 패키지 기술인 '엑스 큐브(X-Cube)'를 적용한 테스트칩 생산에 성공했다고 13일 밝혔다. 엑스 큐브는 여러 반도체 칩을 위로 적층(3D)해 면적 효율을 끌어올리는 후공정 기술이다. 기존에는 평면(2D)으로 나란히 배치했다.

삼성전자는 이번 신기술을 통해 고객사 유치에도 적극 나선다. 글로벌 팹리스들은 삼성전자 엑스-큐브 설계방법론 등을 활용해 EUV 기반 5나노·7나노 공정 칩 개발을 바로 시작할 수 있다.

이미지 확대보기

이미지 확대보기그간 삼성전자는 파운드리 1위 TSMC를 따라잡기 위해 전공정에 해당하는 초미세 공정 기술에 집중해왔다.

그러나 상대적으로 후공정(패키지) 분야에 대한 기술 투자가 지지부진 했던 것이 지금의 격차를 만든 이유 중 하나로 꼽힌다. 삼성전자가 밝힌 것처럼 차세대 패키지 기술이 반도체 성능에 직접적인 영향을 주기 시작했기 때문이다. TSMC는 5나노 공정에 적용할 차세대 패키지 기술 'SolC'를 내년 공개할 것으로 알려졌다.

이에 삼성전자도 지난해 삼성전기 PLP 사업부를 인수하는 등 패키지 기술 강화에 속도를 내기 시작했다.

삼성전자 관계자는 "이번 기술로 최첨단 EUV 초미세 전공정뿐 아니라 후공정에서도 첨단 기술 경쟁력을 확보하게 됐다"며 "반도체 비전 2030을 달성하는데 큰 역할을 할 것"이라고 밝혔다.

이미지 확대보기

이미지 확대보기곽호룡 기자 horr@fntimes.com

[관련기사]

가장 핫한 경제 소식! 한국금융신문의 ‘추천뉴스’를 받아보세요~

데일리 금융경제뉴스 Copyright ⓒ 한국금융신문 & FNTIMES.com

저작권법에 의거 상업적 목적의 무단 전재, 복사, 배포 금지

![현대차 저평가 굴레, AI로봇 아틀라스가 끊을까 [Z-기업가치 바로보기]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=20260315225623018140dd55077bc221924192220.jpg&nmt=18)

![삼성전기 장덕현, MLCC·기판 업고 영업익 2조 ‘정조준’ [AI특수 숨은 알짜들 ①]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=2026030900142007208dd55077bc221924192196.jpg&nmt=18)

![박인원의 ‘휴머노이드 선언’...두산 ‘3차 대변신’ 이끌까 [K-휴머노이드 대전] ③ ‘오너 4세’ 주도 두산로보틱스](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=2026030120284507035dd55077bc212411124362.jpg&nmt=18)

![[DQN] ‘김동선 체제 4년’ 한화갤러리아, 사업확장 했지만 돈은 못 벌었다 [Z스코어 기업가치 바로보기]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=2026030120193900218dd55077bc212411124362.jpg&nmt=18)

![美서 건너온 ‘아틀라스ʼ냐, 국대 2족보행 ‘휴보ʼ냐 [휴머노이드, 우리가 만든다]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=110&h=79&m=5&simg=20260316002604050900dd55077bc221924192220.jpg&nmt=18)

![‘주주환원・AI 전환’, 두 마리 토끼 잡는 SK네트웍스 [자사주 리포트]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=110&h=79&m=5&simg=202603191051550460007fd637f54312411124362.jpg&nmt=18)