이미지 확대보기

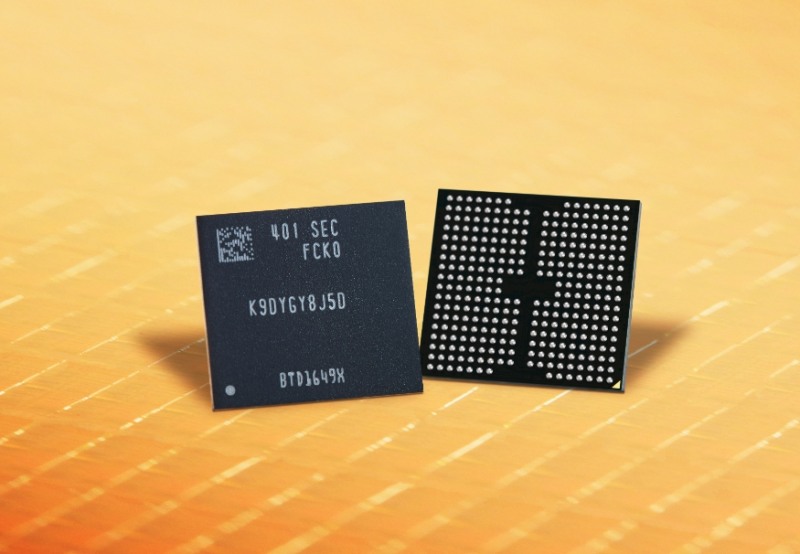

이미지 확대보기TLC는 하나의 셀에 3bit(비트) 데이터를 기록할 수 있는 구조다. 삼성전자는 ▲업계 최소 크기 셀(Cell) ▲최소 몰드(Mold) 두께를 구현해 '1Tb TLC 9세대 V낸드'의 비트 밀도(Bit Density)를 이전 세대 대비 약 1.5배 증가시켰다.

삼성전자의 '9세대 V낸드'는 더블 스택(Double Stack) 구조로 구현할 수 있는 최고 단수 제품이다. '채널 홀 에칭(Channel Hole Etching)' 기술을 통해 한번에 업계 최대 단수를 뚫는 공정 혁신을 이뤄 생산성도 향상됐다.

채널 홀 에칭이란 몰드층을 순차적으로 적층한 다음 한번에 전자가 이동하는 홀(채널 홀)을 만드는 기술이다. 적층 단수가 높아져 한번에 많이 뚫을수록 생산효율 또한 증가하지만 정교화·고도화 기술이 요구된다.

9세대 V낸드는 차세대 낸드플래시 인터페이스인 'Toggle 5.1'이 적용돼 8세대 V낸드 대비 33% 향상된 최대 3.2Gbps의 데이터 입출력 속도를 구현했다.

삼성전자는 이를 기반으로 PCIe 5.0 인터페이스를 지원하고 고성능 SSD 시장을 확대해 낸드플래시 기술 리더십을 공고히 할 계획이다.

9세대 V낸드는 저전력 설계 기술을 탑재해 이전 세대 제품 대비 소비 전력이 약 10% 개선됐다. 환경 경영을 강화하면서 에너지 비용 절감에 집중하는 고객들에게 최적의 솔루션이 될 것으로 기대된다.

삼성전자는 이어 올 하반기 'QLC(Quad Level Cell) 9세대 V낸드'도 양산할 예정이다.

홍윤기 한국금융신문 기자 ahyk815@fntimes.com

가장 핫한 경제 소식! 한국금융신문의 ‘추천뉴스’를 받아보세요~

데일리 금융경제뉴스 Copyright ⓒ 한국금융신문 & FNTIMES.com

저작권법에 의거 상업적 목적의 무단 전재, 복사, 배포 금지

![현대차 저평가 굴레, AI로봇 아틀라스가 끊을까 [Z-기업가치 바로보기]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=20260315225623018140dd55077bc221924192220.jpg&nmt=18)

![삼성전기 장덕현, MLCC·기판 업고 영업익 2조 ‘정조준’ [AI특수 숨은 알짜들 ①]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=2026030900142007208dd55077bc221924192196.jpg&nmt=18)

![박인원의 ‘휴머노이드 선언’...두산 ‘3차 대변신’ 이끌까 [K-휴머노이드 대전] ③ ‘오너 4세’ 주도 두산로보틱스](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=2026030120284507035dd55077bc212411124362.jpg&nmt=18)

![[DQN] ‘김동선 체제 4년’ 한화갤러리아, 사업확장 했지만 돈은 못 벌었다 [Z스코어 기업가치 바로보기]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=2026030120193900218dd55077bc212411124362.jpg&nmt=18)

![삼성전자 200조 벌면 주주환원도 5배 늘어날까 [자사주 리포트]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=284&h=214&m=5&simg=202603131930130953307de3572ddd12517950139.jpg&nmt=18)

![美서 건너온 ‘아틀라스ʼ냐, 국대 2족보행 ‘휴보ʼ냐 [휴머노이드, 우리가 만든다]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=110&h=79&m=5&simg=20260316002604050900dd55077bc221924192220.jpg&nmt=18)

![SKC 김종우 머릿속엔 온통 ‘유리기판’ 뿐 [AI 특수 숨은 알짜들 ②]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=110&h=79&m=5&simg=20260316001810017500dd55077bc221924192220.jpg&nmt=18)

![현대차 저평가 굴레, AI로봇 아틀라스가 끊을까 [Z-기업가치 바로보기]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=110&h=79&m=5&simg=20260315225623018140dd55077bc221924192220.jpg&nmt=18)

![삼성전자 200조 벌면 주주환원도 5배 늘어날까 [자사주 리포트]](https://cfnimage.commutil.kr/phpwas/restmb_setimgmake.php?pp=006&w=110&h=79&m=5&simg=202603131930130953307de3572ddd12517950139.jpg&nmt=18)